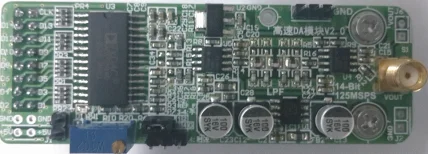

Greitųjų DA AD9764 Modulio 14-bitų Lygiagrečią DA 125M Signalo Kartos FPGA Plėtros Taryba

Nauja

Yra sandėlyje

Žymos: žemo dažnio signalas, spartan6, altera fpga, fpga, altera, kurti valdybos fpga, xilinx fpga, valdybos fpga, xilinx, 1200w valdyba.

modname=ckeditor

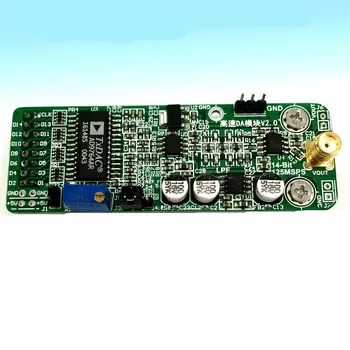

AD9764 didelės spartos DA modulis V2.0

Greitųjų DA modulis pasirenka 14bit didelės spartos DA converter AD9764 LPN Bendrovė, ėminių ėmimo dažnis AD9764 yra iki 125MSPS, ir vidaus nuoroda įtampa yra on-chip, kurie atitinka pramonės srityse.Modulis susideda iš signalų 16PIN skaitmeninė sąsaja, didelės spartos DA konversijos, diferencialas vieno baigėsi, 7-ryšys pasyvus filtravimo, signalo stiprinimo, signalo išvesties sąsaja ir galios valdymo (+5 V į 5 V ir 3,3 V) ir kt.Bendroji schema modulis yra taip:

(1) mėginių Ėmimo dažnis: iki 125MSPS.

(2) amplitudės vertė analoginio signalo išėjimas: 600mV~6 V (±300mV~±3V).

(3) Analoginis signalas, dažnių juostos plotis (6Vpp):

①The dažnių išėjimo elipsės filtras: -1dB. dažnių juostos plotis yra apie 14MHz, -3dB dažnių juostos plotis yra apie 26MHz.

②The dažnių išėjimo Beselio filtrų: -1dB. dažnių juostos plotis yra apie 7MHz, -3dB dažnių juostos plotis yra apie 13MHz.

(4) Skaitmeninė sąsaja lygis: 3.3 V.

(5) Modulis maitinimo įtampa: +5V vieno maitinimo šaltinio.

(6) analoginis signalas išėjimo sąsaja priima dviejų rūšių: vienos yra 2.54 pikis pin sąsaja, ir kitas yra SMA interface (numatytasis).

(7) Skaitmeniniai signalų sąsaja: 2 x 8 dvigubo eilės 2.54 pikis moterų sėdynės, kryptimi žemyn.

(8) Modulis, D/A konvertavimo įtampos nuoroda ryšį priima trys būdai: naudoti AD9764 on-chip įtampos nuoroda (pagal nutylėjimą); naudoti potenciometras ant modulio koreguoti; naudoti išorinę įvestį.

(9) Šis modulis yra skirtas lizdas, GND, kuris yra naudojamas prijungti įžeminimo zondas iš multimetro palengvinti vartotojo bandymai.

(10) elipsės formos filtro versija arba Besselio filtro versija, galima pasirinkti pagal faktinį vartotojo poreikius; elipsės formos filtro versija yra tiesiogiai susiduria sine bangų signalo išėjimas, ir aikštėje banga ir trikampio banga produkcija turi peržengti ne auga arba mažėja kraštą; Kad Searle filtro versija yra, kuria siekiama kvadratinių bangų ir trikampio banga produkcija.Nėra situacijas, dėl didėjančios arba mažėjančios krašto signalas, tačiau sine wave išėjimo dažnių juostos plotis bus paveikti.

Analoginis signalas išėjimo sąsaja priima dviejų rūšių, vienas iš jų yra pin sąsaja ir kitas yra SMA interface (SMA interface rekomenduojama įvesties signalai); duomenų sąsaja priima 16PIN 2.54 pikis moterų sąsaja.Sąsajos modulis yra rodomi toliau pateikiamame paveikslėlyje:

Bandymo didelės spartos DA modulis turi naudoti DA konversijos valdytojas (paprastai naudoti FPGA), +5V linijinių reguliuojamos elektros energijos tiekimo (mažos pulsacijos) ir signalo šaltinio.Naudoti linijinės stabilizuotas maitinimo modulis, C8051F/STM32 +FPGA core valdybos ir 200MHz oscilloscope parduotuvėje statyti bandymų jungimo schema, kaip parodyta paveikslėlyje, žemiau.

Modulio derinimo poveikis

Bandymo sąlygos, bandymo pasirenka vidaus nuoroda 1.2 V, ir modulio galia peak-to-peak vertė yra apie 6 V.Išvesties amplitudės-dažnio charakteristika, duomenys sine wave (elipsės filtras) yra parodyta lentelėje žemiau.

Dažnis

100Hz

1kHz

10kHz

100kHz

1MHz

2MHz

Amplitudemv

6120

6120

6160

6160

6160

6160

Dažnis

3MHz

4MHz

5MHz

6MHz

7MHz

8MHz

Amplitudemv

6120

6080

6040

6000

5960

5880

Dažnis

9MHz

10MHz

11MHz

12MHz

13MHz

14MHz

Amplitudemv

5840

5800

5760

5720

5640

5600

Dažnis

15MHz

16MHz

17MHz

18MHz

19MHz

20MHz

Amplitudemv

5520

5440

5400

5280

Penkių tūkstančių dviejų šimtų

5080

Dažnis

21MHz

22MHz

23MHz

24MHz

25MHz

26MHz

Amplitudemv

5000

4920

4800

4640

4520

4400

Dažnis

27MHz

28MHz

29MHz

30MHz

31MHz

32MHz

Amplitudemv

4160

3880

3560

3200

2760

2280

Dažnis

33MHz

34MHz

35MHz

Amplitudemv

1760

1360

1040

Sinusinės bangos signalo išėjimas poveikis diagramoje:

Kvadratinių bangų signalo išėjimas poveikis diagramoje:

Trikampio banga signalo išėjimas poveikis diagramoje:

Pastaba: Dėl išėjimo iš aikštės banga ir trikampio bangos signalas, dėl savybes elipsės filtrą, įkalnės ir nuokalnės kraštų išėjimo signalas turės peržengti.Auga krašto plėtros schema yra parodyta paveiksle, ir signalas yra akivaizdus viršijimo.

Yra versija kvadratinių bangų ir trikampio banga produkcija.Filtras yra Besselio filtro, ir auga arba mažėja krašto išėjimo kvadratinių bangų ir trikampio banga neturi peržengti.Tačiau, atsižvelgiant į savybes, Beselio filtrų, pralaidumą sine bangų, produkcija bus paveikti.Ir-1dB. pralaidumą sine wave " modulis yra apie 7MHz, ir -3dB dažnių juostos plotis yra apie 13MHz.Kai signalas yra didesnis nei 20MHz, signalo, bus jitter (vaizdo dažnis Nėra filtruojamas).Auga krašto aikštės banga išėjimo Besselio filtro yra parodyta paveiksle, ir auga krašto yra švelnus ir be viršijimo.

AD9764 didelės spartos DA modulis

Naudojimo instrukcijos, modulio schema (pdf versija), FPGA bandymų programa ir chip vadovas

Nė vienas klientas komentarus šiuo metu.